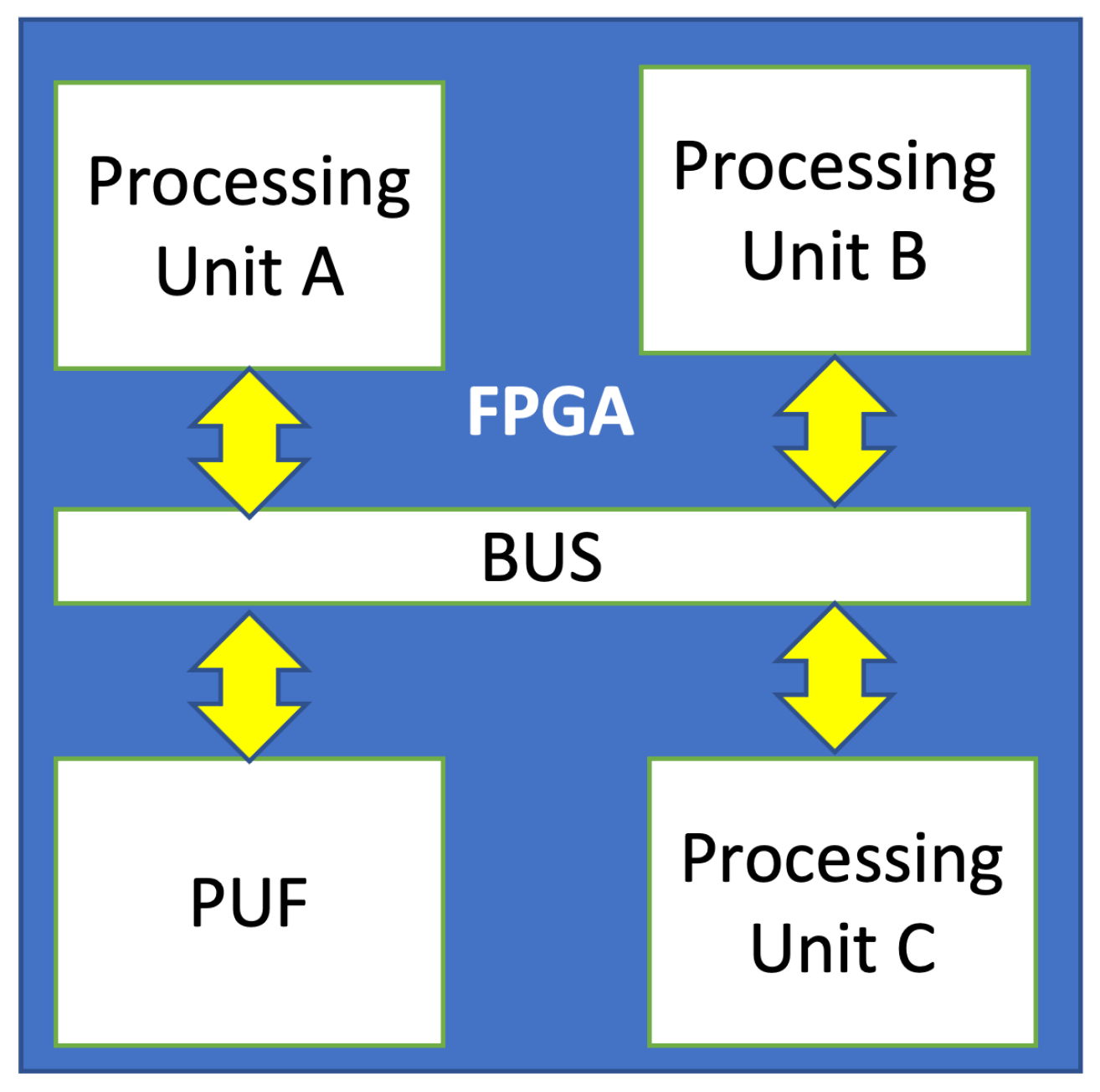

Multi-mode PUF used for FPGA firmware Trojan detection Conclusion A new... | Download Scientific Diagram

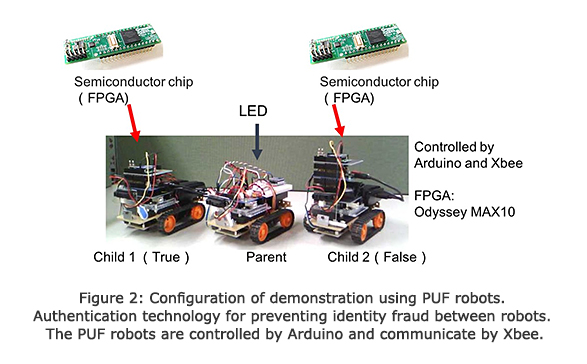

Toshiba Develops Mutual Authentication Technology for IoT Devices by PUF Fingerprinting Using Variations in Semiconductor Chips | Corporate Research & Development Center | Toshiba

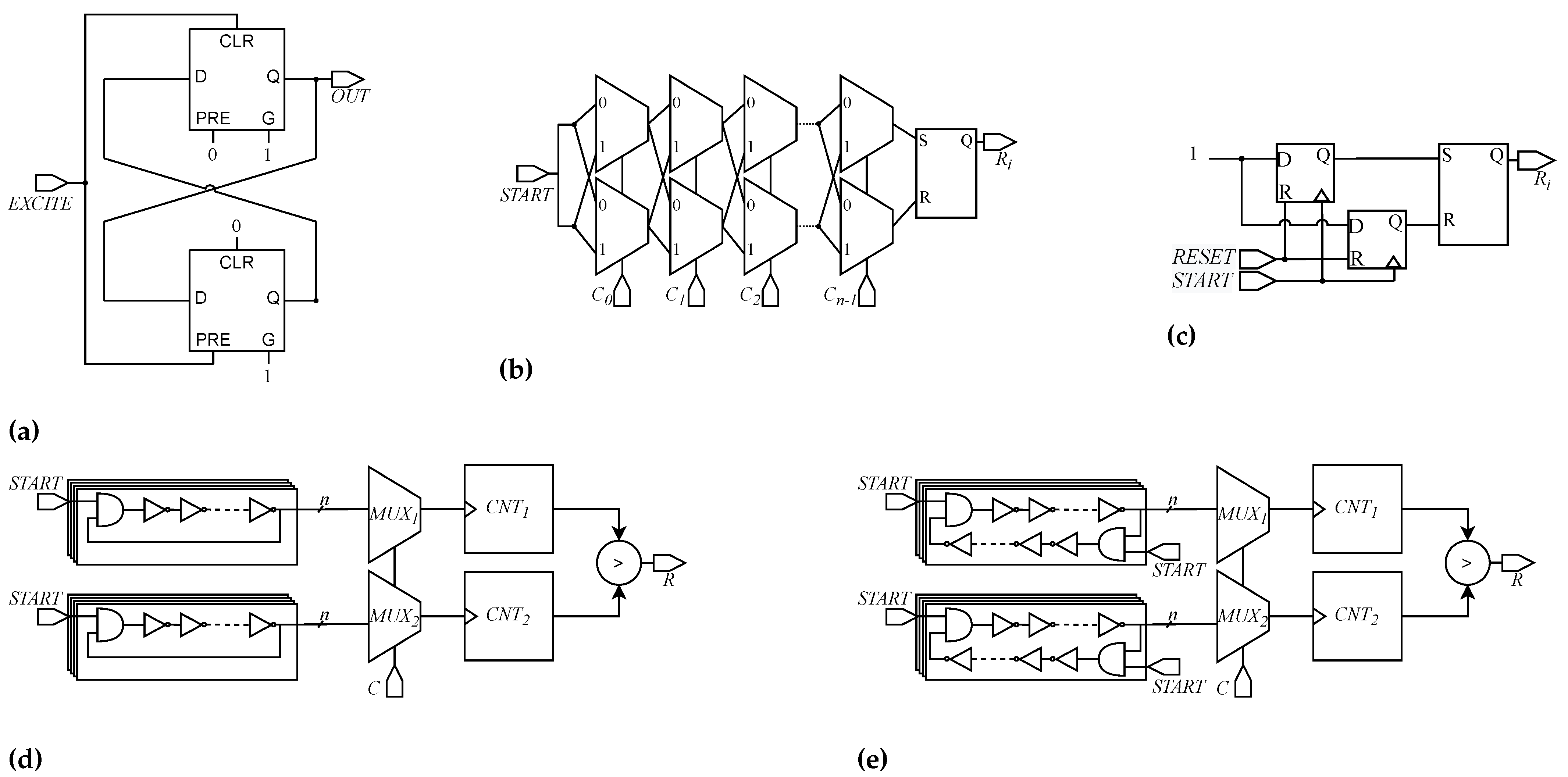

Partial bitstream protection for low-cost FPGAs with physical unclonable function, obfuscation, and dynamic partial self reconfiguration - ScienceDirect

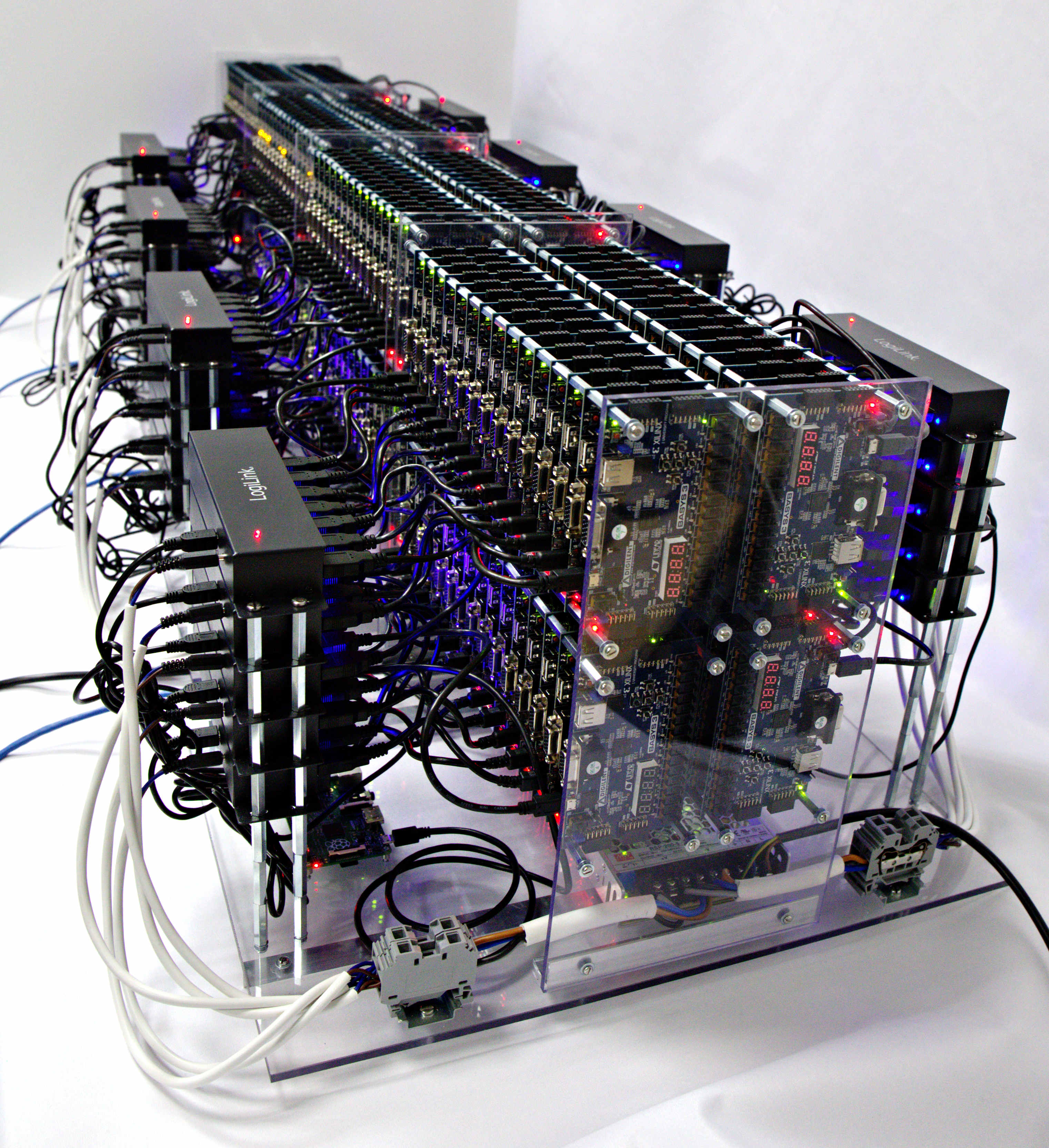

Intrinsic ID Announces Embedded SRAM PUF Security IP for Military-Grade IP protection in Intel FPGAs